propiedades del producto:

| ESCRIBE | DESCRIBIR |

| categoría | Circuito Integrado (CI) Embebido - Microcontroladores |

| fabricante | NXP EE. UU. Inc. |

| serie | MPC56xx Qorivva |

| Paquete | bandeja |

| Estado del producto | en stock |

| procesador central | e200z0h |

| Especificación del núcleo | Núcleo único de 32 bits |

| velocidad | 64 MHz |

| Conectividad | Bus CAN, FlexRay, LINbus, SPI, UART/USART |

| Periféricos | DMA, POR, PWM, WDT |

| Número de E/S | 108 |

| Capacidad de almacenamiento de programas | 512KB (512K x 8) |

| Tipo de memoria de programa | destello |

| capacidad EEPROM | 64Kx8 |

| Tamaño de RAM | 40Kx8 |

| Voltaje - Fuente de alimentación (Vcc/Vdd) | 3V ~ 5.5V |

| convertidor de datos | A/D 30x10b |

| Tipo de oscilador | interno |

| Temperatura de funcionamiento | -40°C ~ 125°C (TA) |

| tipo de instalación | Tipo de montaje en superficie |

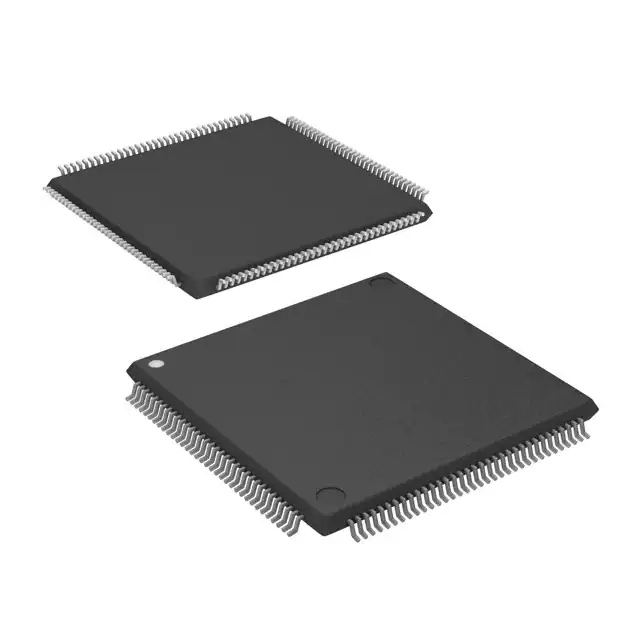

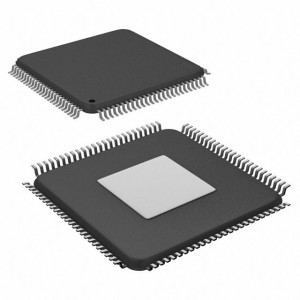

| Paquete/Recinto | 144-LQFP |

| Embalaje del dispositivo del proveedor | 144-LQFP(20x20) |

| Número de producto básico | SPC5604 |

Medio Ambiente y Clasificación de las Exportaciones:

| ATRIBUTOS | DESCRIBIR |

| Estado RoHS | Cumple con la especificación ROHS3 |

| Nivel de sensibilidad a la humedad (MSL) | 3 (168 horas) |

| REACH estado | Productos fuera de REACH |

| ESCAPAR | 3A991A2 |

| HTSUS | 8542.31.0001 |

Resumen del bloque de la serie MPC5604P:

función de bloque

Convertidor de analógico a digital (ADC) Convertidor de analógico a digital multicanal de 10 bits

Módulo de asistencia de arranque (BAM) Bloque de memoria de solo lectura que contiene código VLE que se ejecuta de acuerdo con

el modo de arranque del dispositivo

Módulo de generación de reloj

(MC_CGM)

Proporciona la lógica y el control necesarios para la generación de sistemas y periféricos.

relojes

Red de área del controlador (FlexCAN) Admite el protocolo de comunicaciones CAN estándar

Unidad de activación cruzada (CTU) Permite la sincronización de conversiones ADC con un evento de temporizador de eMIOS

o del PIT

Conmutador de barra cruzada (XBAR) Admite conexiones simultáneas entre dos puertos maestros y tres esclavos

puertos;admite un ancho de bus de direcciones de 32 bits y un ancho de bus de datos de 32 bits

Comprobación de redundancia cíclica (CRC) Generador de suma de comprobación CRC

Interfaz periférica serial Deserial

(DSPI)

Proporciona una interfaz serial síncrona para la comunicación con dispositivos externos

Acceso directo mejorado a la memoria

(eDMA)

Realiza transferencias de datos complejas con una intervención mínima de un procesador host

a través de “n” canales programables

Temporizador mejorado (eTimer) Proporciona un módulo de conteo ascendente/descendente programable mejorado

Módulo de estado de corrección de errores

(ECSM)

Proporciona una gran variedad de funciones de control misceláneas para el dispositivo, incluidas

información visible del programa sobre los niveles de configuración y revisión, un reinicio

registro de estado, control de activación para salir de los modos de suspensión y características opcionales

como información sobre errores de memoria informados por códigos de corrección de errores

Oscilador externo (XOSC) Proporciona un reloj de salida utilizado como referencia de entrada para FMPLL_0 o como referencia

reloj para módulos específicos dependiendo de las necesidades del sistema

Unidad de recolección de fallas (FCU) Proporciona seguridad funcional al dispositivo

Memoria flash Proporciona almacenamiento no volátil para código de programa, constantes y variables

Frecuencia modulada

bucle de enganche de fase (FMPLL)

Genera relojes de sistema de alta velocidad y admite frecuencia programable

modulación

Controlador de interrupción (INTC) Proporciona programación preventiva basada en prioridades de solicitudes de interrupción

Controlador JTAG Proporciona los medios para probar la funcionalidad y conectividad del chip mientras permanece

transparente a la lógica del sistema cuando no está en modo de prueba

Controlador LINFlex Gestiona una gran cantidad de mensajes LIN (protocolo de red de interconexión local)

eficientemente con una carga mínima en la CPU

Módulo de entrada de modo (MC_ME) Proporciona un mecanismo para controlar el modo de funcionamiento y el modo de funcionamiento del dispositivo.

secuencias de transición en todos los estados funcionales;también gestiona la unidad de control de potencia,

restablecer el módulo de generación y el módulo de generación de reloj, y mantiene el

registros de configuración, control y estado accesibles para las aplicaciones

Temporizador de interrupción periódica (PIT) Produce interrupciones y disparadores periódicos

Puente periférico (PBRIDGE) Interfaz entre el bus del sistema y los periféricos en chip

Unidad de control de potencia (MC_PCU) Reduce el consumo total de energía al desconectar partes del dispositivo

de la fuente de alimentación a través de un dispositivo de conmutación de alimentación;los componentes del dispositivo son

agrupados en secciones denominadas “dominios de poder” que son controlados por la UCP